Silicon Valley at a glance

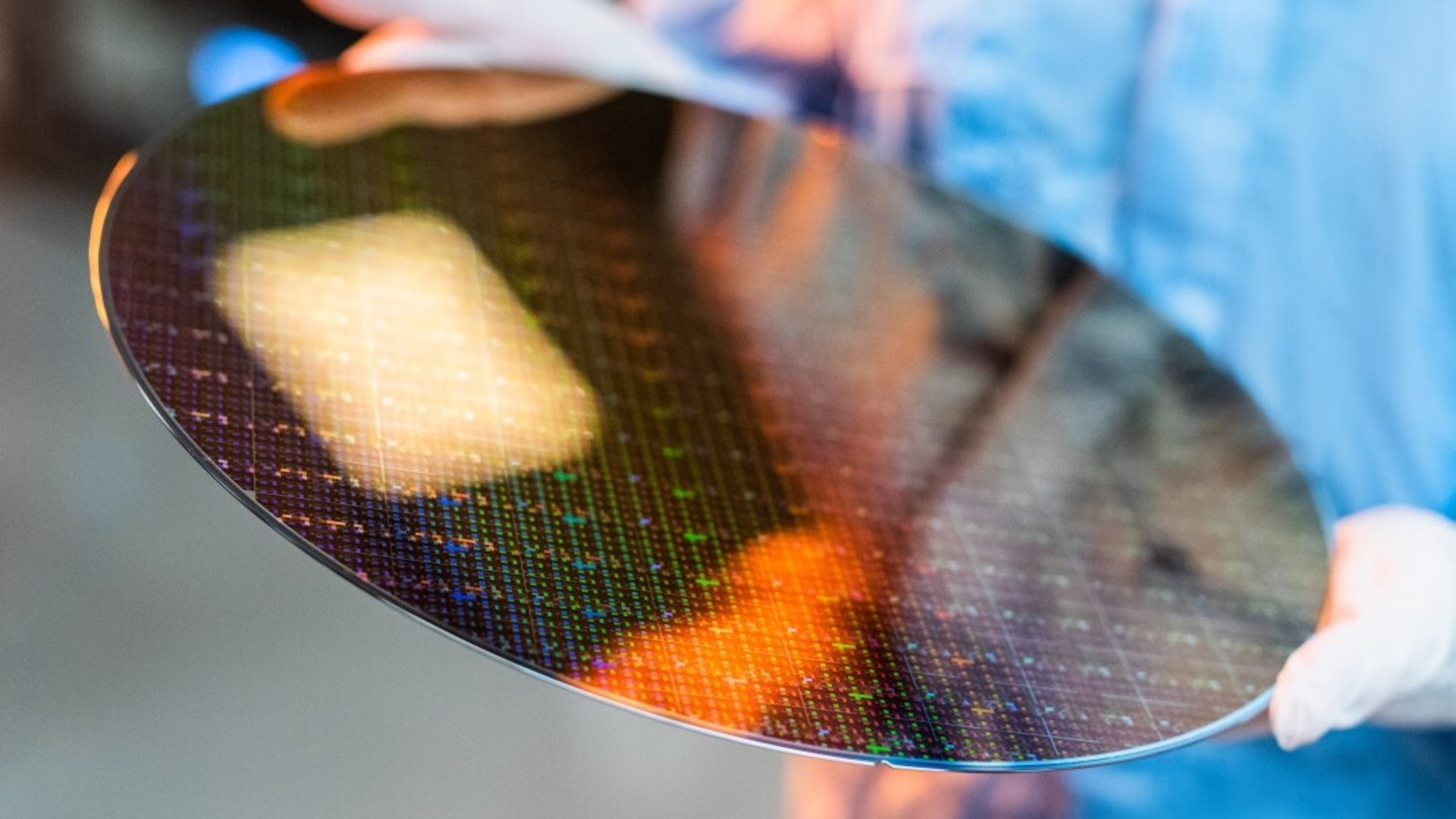

ASML Silicon Valley, located in San Jose, develops sophisticated software and metrology solutions for chipmakers, enabling ASML’s holistic lithography approach.

0123456789

0123456789

0123456789

0123456789

Year acquired Brion

0123456789

0123456789

0123456789

0123456789

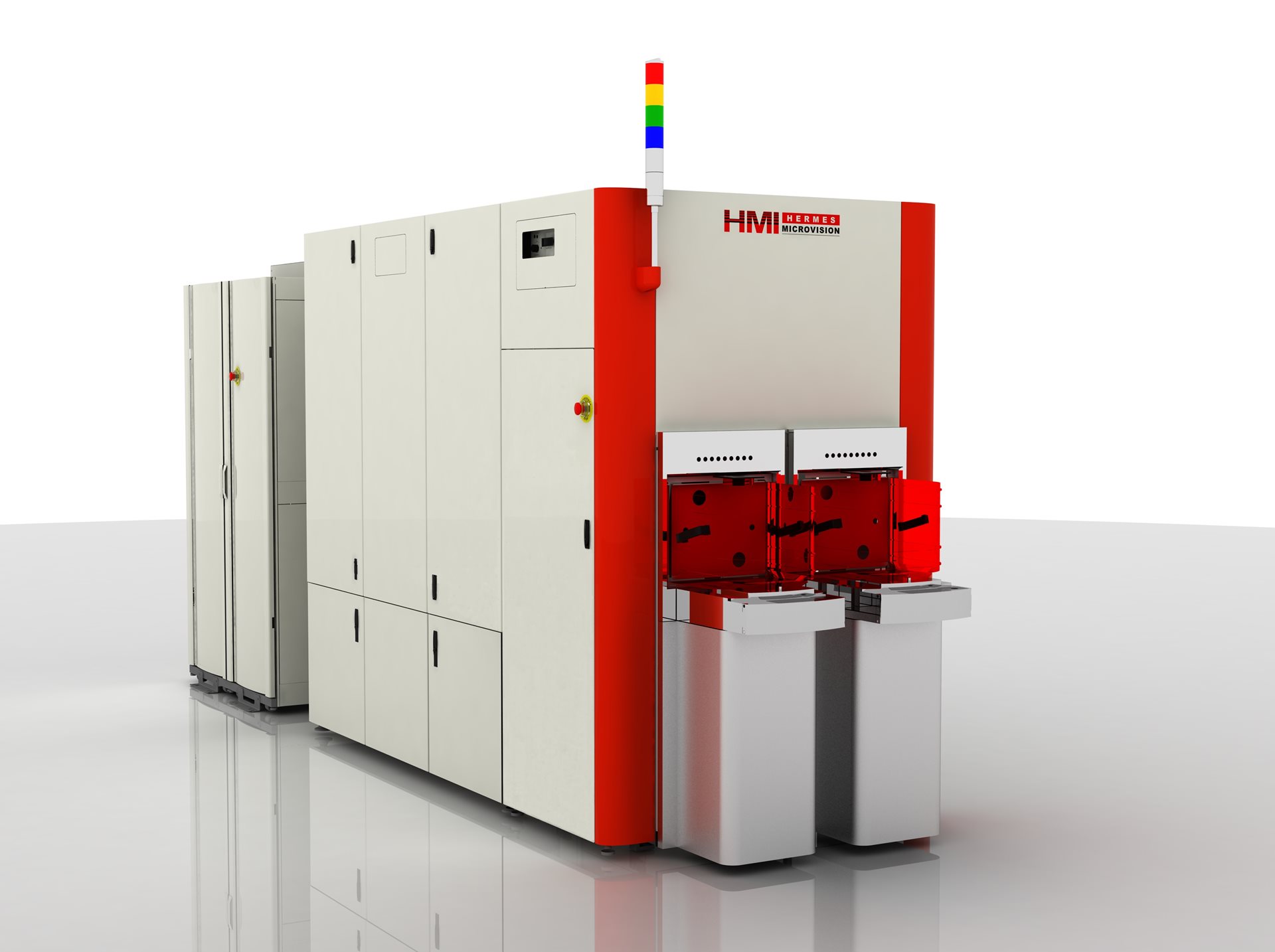

Year acquired HMI

0123456789

k

+

Employees

2022 annual figures

0123456789

y

e

a

r

s

Average employee tenure

2022 annual figures

Specialties

Find your passion at ASML Silicon ValleyOur technology in Silicon Valley

At ASML Silicon Valley, we develop sophisticated software and metrology solutions, addressing escalating complexities encountered at smaller nodes. Local customer support and technology development also ensure superior system performance and service.

Read more

Working and living in Silicon Valley

ASML Silicon Valley is located in San Jose, California – a dynamic area where technology and culture converge in a fast-paced, innovative environment. The third most populous city in California, San Jose ranks as one of the wealthiest cities in the United States.

Read more

Software heroines

Leading the way for women in ICT at ASML

Read about Mingjing Zhao, a senior software quality assurance manager at ASML in Silicon Valley, and other women as they pursue their dreams in computer science and software engineering at ASML.

"We are often the pioneer and pilot team for new ideas. That is what makes the Silicon Valley sectors very unique.”

"The Silicon Valley site works together with colleagues around the world to deliver a holistic solution to customers by providing our unique competency."

"At the Silicon Valley site, we make software that is used for the research and development stage in the manufacturing process. Before our customers mass produce their chips, they need our software to help improve and optimize their process.”

"We are at the forefront of the technology, so every day we are dealing with a problem that will not actually have impact for today, but it will have impact in for the near future.”

Browse jobs in Silicon Valley

Discover what ASML has to offer in San Jose.

Want to be alerted for new jobs?

Create job alert