Announcement - San Jose, California, August 20, 2021

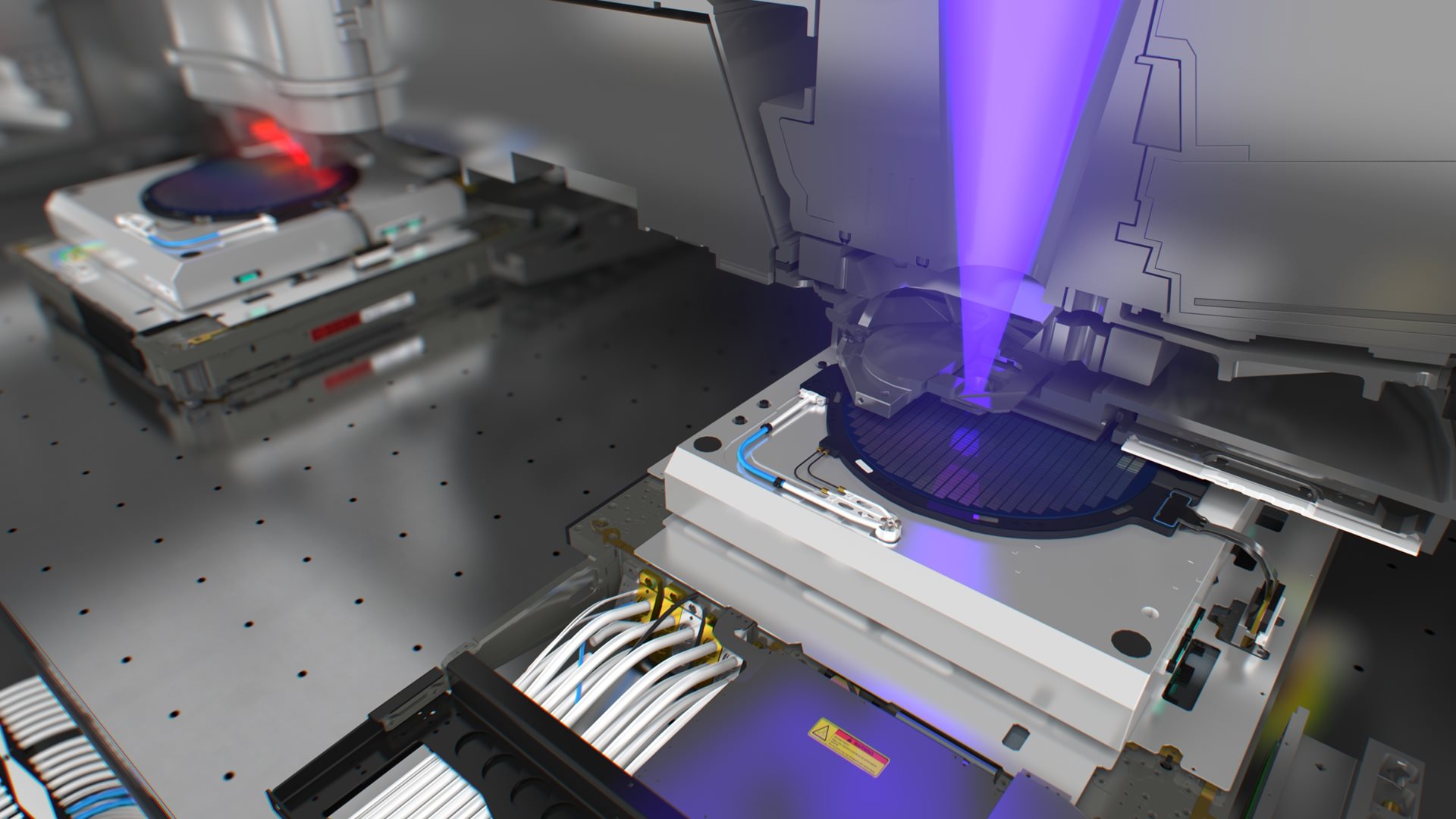

On Friday, August 20, 2021, ASML welcomed employees, local public officials and the media to the opening celebration of its new campus in Silicon Valley, California. The 212,573-square-foot facility includes a Class 1000 cleanroom, lab space and collaboration areas to advance ASML’s holistic lithography portfolio – hardware, software and services used to generate circuit patterns on silicon in high-volume production of microchips.

It’s no longer enough to address the various semiconductor manufacturing steps in isolation. The Silicon Valley team co-optimizes IC designs, photomasks, lithography, and metrology and inspection to enhance manufacturability and yield of leading-edge semiconductors through its expertise in computational lithography and e-beam metrology and inspection.

“As chipmakers continue to shrink the patterns to make small and powerful chips, we continue to grow to address the escalating complexities that require ever-more sophisticated approaches,” said Jim Koonmen, executive vice president of Applications Business at ASML. “It would be impossible to manufacture at dimensions of 10 nm or smaller without our software and metrology solutions, and we have a long-term roadmap to help our customers overcome their future chip production challenges.”

ASML expands footprint in the Valley and prepares for hiring ramp-up

ASML first established its presence in Silicon Valley 20 year ago and now more than 875 employees work at the new campus. In addition, the team plans to grow 20% in 2022, hiring more than 180 engineers to execute its product roadmap and meet the insatiable demand for more microchips.

“Our region is ripe with smart, skilled workers and the demand in the semiconductor industry is only growing,” said Yu Cao, CEO of HMI at ASML. “Our expansion is critical to not only supporting our product development and future growth, but providing a modern, collaborative workspace that helps attract and retain top talent.”

Previously, the two product groups (Brion and HMI) worked in different buildings separated by a short car ride, which impeded collaboration and technology integration. As the teams have ramped up prototype development for a new product line – multi-beam e-beam technology – over the last year, they quickly outgrew the existing lab and cleanroom space to meet their aggressive engineering timelines.

Additionally, local customer support teams engage directly with chipmakers in the Silicon Valley region to ensure superior system performance and service. The ASML Technology Development Center focuses on research efforts to support the long-term product roadmap.

New cleanroom and lab space critical to prototype development

The new campus features a 24,000-square-foot state-of-the-art cleanroom and lab space, which will be critical for enabling the next generation of e-beam technology development as well as ongoing product improvements. This includes research in mechanical, optical and analog engineering, as well as testing, mechatronics and more.

Today’s mainstream optical inspection technologies are reaching their resolution limits. With its high image resolution, e-beam metrology technology is becoming necessary to achieve accurate measurements and address shrinking margins of error.

In Silicon Valley, we’re creating a new class of applications to ensure accurate wafer patterning performance and identify yield-related defects faster with higher accuracy across more wafers at the most advanced nodes.

Deep learning algorithms and advanced metrology enable continued scaling

Ultimately, it’s all about optimizing scanner, masks and processes for device manufacturability and yield, both early in design and technology development and later during high-volume production.

ASML is expanding the power of computation from lithography to optical metrology and e-beam inspection, as well as machine learning applications. The Silicon Valley team plans to continue to link its metrology and inspection systems with ASML’s lithography systems, leveraging expertise in both fields.

“In order to meet the next decade of scaling challenges, we need our Brion and HMI engineers to engage in an open exchange of product concepts, designs and value propositions,” said Stan Baron, general manager of Brion at ASML. “Our new campus is purposefully built with this goal in mind.”

ASML already used high-resolution e-beam images from e-beam metrology systems to improve the accuracy of its computational lithography models down to the single-nanometer level to support imaging of ever-smaller features. These improved models are then used to enhance scanner control, improving yield.

ASML’s software and HMI’s hardware technologies are complementary, and when combined offer the chance to significantly improve process control and yield for our customers, which comprise all the world’s top chipmakers.

Together, ASML Silicon Valley will create a new class of applications to help chipmakers achieve higher manufacturing yields as they move to 10 nm node and beyond – an unparalleled level of automated, continuous process control over the lithography patterning process.

Explore open ASML jobs in Silicon Valley to be part of developing our next big advancement.

About ASML