Press release - Veldhoven, the Netherlands, October 15, 2008

ASML Holding NV (ASML) today unveiled innovations in its TWINSCAN lithography platform that offer significant improvements in overlay and productivity, enabling the semiconductor industry to continue its roadmap for more advanced and affordable chips. The TWINSCAN NXT platform, presented to the media at the ASML Research Review, is also suited for emerging double-patterning techniques which manufacturers need to shrink the smallest chip features by up to 42%.

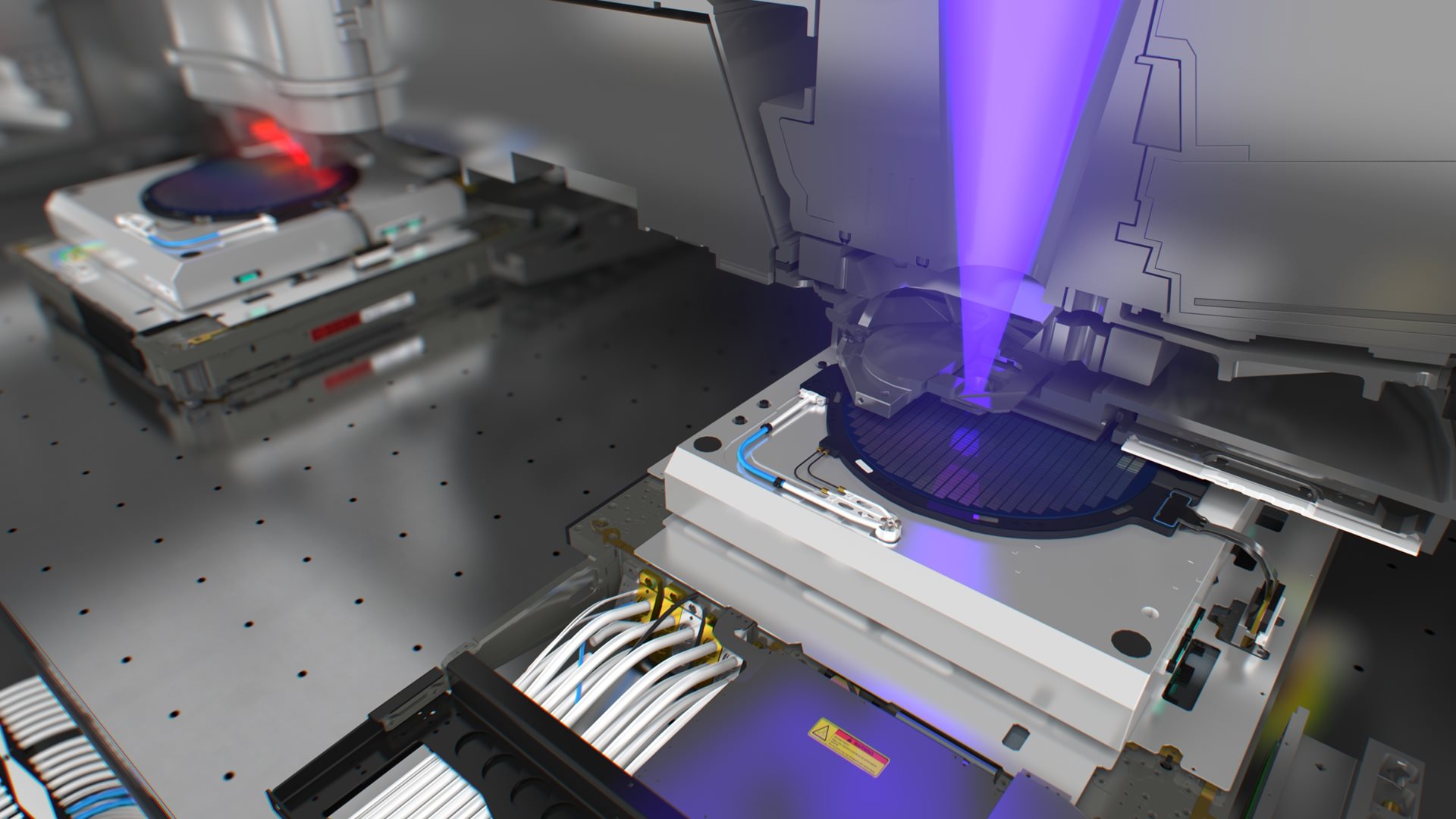

The TWINSCAN NXT platform features a new planar wafer stage design, extending the modular TWINSCAN architecture (of which almost 900 systems have been sold) for multiple generations of ASML lithography machines. Providing a baseline for further performance upgrades, the new wafer stage technology is key to continuing the trend of aggressive chip cost reductions well into the future.

Thanks to a new concept and innovative materials, the wafer stage is considerably lighter than previous generations. This, in combination with an elegant design that reduces overhead, enables high acceleration for shorter positioning (stepping) times. As a result, the platform will initially improve productivity by more than 30%.

In addition, a new positioning measurement system positions the wafer stage even more accurately than in current systems. The resulting overlay improvement of 50% will help manufacturers gain better control of their process so they can produce more good chips per wafer and further shrink transistor sizes.

“Feature shrink drives the semiconductor industry forward by enabling smaller chips with greater functionality and lower power consumption,” says Martin van den Brink, ASML’s executive vice president of marketing and technology. “Our new systems bring improvements that will help chipmakers image smaller features. Better wafer positioning delivers more imaging control and better overlay. In combination with improved productivity, the TWINSCAN NXT platform opens the road to double-patterning techniques that allow chip manufacturers over time to use existing immersion lithography technology for volume production at the 32-nanometer node and beyond.”

About the TWINSCAN platform

About wafer stage technology

About immersion lithography

About double patterning

About ASML